43

在第五章中,我们讨论了 PCB 传输线阻抗特性。其实,在更高

的频率下,阻抗会更加复杂。玻纤布环氧树脂层压系统是各向异性的,

玻纤布和树脂的特性不同,信号在树脂或玻纤束周围传播时,阻抗会

产生变化。

自 2015 年以来,我一直在研究和教导其他人有关玻纤编织效应

(GWS) 相关的知识。我看到一些硬件团队在设计高速信号布线时忽

略了这一点,因为样机工作正常。还有一些团队喜欢使用某一种特定

的解决方案来减轻玻纤编织效应,而忽略了其他成本更低的选项。如

果您的团队情况类似,那么本章的内容应该会很有帮助。

差分 Skew

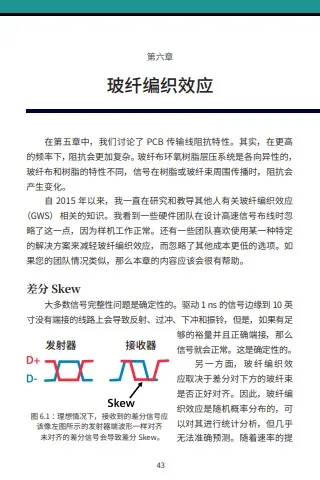

大多数信号完整性问题是确定性的。驱动 1 ns 的信号边缘到 10 英

寸没有端接的线路上会导致反射、过冲、下冲和振铃,但是,如果有足

够的裕量并且正确端接,那么

信号就会正常。这是确定性的。

另 一 方 面, 玻 纤 编 织 效

应取决于差分对下方的玻纤束

是否正好对齐。因此,玻纤编

织效应是随机概率分布的,可

以对其进行统计分析,但几乎

无法准确预测。随着速率的提

第六章

玻纤编织效应

图 6.1 :理想情况下,接收到的差分信号应

该像左图所示的发射器端波形一样对齐

未对齐的差分信号会导致差分 Skew。

发射器 接收器

44

高,这种影响会更加复杂。可能样机和 99% 的电路板能正常工作,

但剩下的 1% 会随机出现现场失效。

不同的微环境可能会导致两个差分信号没有对齐,如图 6.1 所

示,并可能导致接收器误解正在发送的数据位。

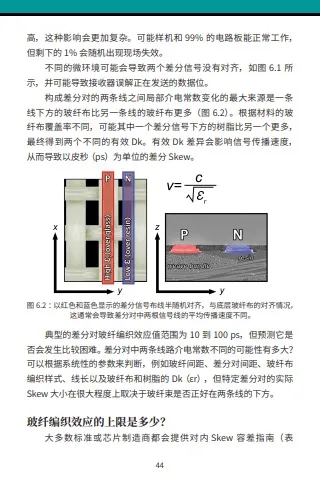

构成差分对的两条线之间局部介电常数变化的最大来源是一条

线下方的玻纤布比另一条线的玻纤布更多(图 6.2)。根据材料的玻

纤布覆盖率不同,可能其中一个差分信号下方的树脂比另一个更多,

最终得到两个不同的有效 Dk。有效 Dk 差异会影响信号传播速度,

从而导致以皮秒 (ps) 为单位的差分 Skew。

典型的差分对玻纤编织效应值范围为 10 到 100 ps,但预测它是

否会发生比较困难。差分对中两条线路介电常数不同的可能性有多大?

可以根据系统性的参数来判断,例如玻纤间距、差分对间距、玻纤布

编织样式、线长以及玻纤布和树脂的 Dk (εr) ,但特定差分对的实际

Skew 大小在很大程度上取决于玻纤束是否正好在两条线的下方。

玻纤编织效应的上限是多少?

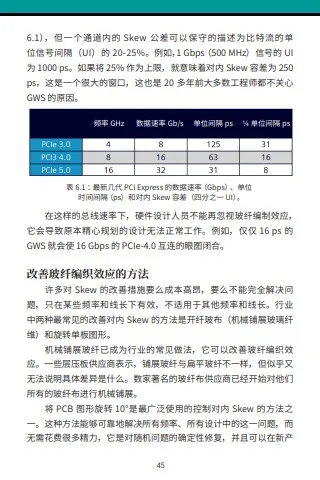

大多数标准或芯片制造商都会提供对内 Skew 容差指南(表

图 6.2 :以红色和蓝色显示的差分信号布线半随机对齐,与底层玻纤布的对齐情况,

这通常会导致差分对中两根信号线的平均传播速度不同。

45

表 6.1 :最新几代 PCI Express 的数据速率 (Gbps) 、单位

时间间隔 (ps) 和对内 Skew 容差(四分之一 UI)。

6.1), 但一个通道内的 Skew 公差可以保守的描述为比特流的单

位信号间隔(UI)的 20-25%。例如,1 Gbps (500 MHz) 信号的 UI

为 1000 ps。如果将 25% 作为上限,就意味着对内 Skew 容差为 250

ps,这是一个很大的窗口,这也是 20 多年前大多数工程师都不关心

GWS 的原因。

在这样的总线速率下,硬件设计人员不能再忽视玻纤编制效应,

它会导致原本精心规划的设计无法正常工作。例如,仅仅 16 ps 的

GWS 就会使 16 Gbps 的 PCIe-4.0 互连的眼图闭合。

改善玻纤编织效应的方法

许多对 Skew 的改善措施要么成本高昂,要么不能完全解决问

题,只在某些频率和线长下有效,不适用于其他频率和线长。行业

中两种最常见的改善对内 Skew 的方法是开纤玻布(机械铺展玻璃纤

维)和旋转单板图形。

机械铺展玻纤已成为行业的常见做法,它可以改善玻纤编织效

应。一些层压板供应商表示,铺展玻纤与扁平玻纤不一样,但似乎又

无法说明具体差异是什么。数家著名的玻纤布供应商已经开始对他们

所有的玻纤布进行机械铺展。

将 PCB 图形旋转 10°是最广泛使用的控制对内 Skew 的方法之

一。这种方法能够可靠地解决所有频率、所有设计中的这一问题,而

无需花费很多精力,它是对随机问题的确定性修复,并且可以在新产

频率 GHz 数据速率 Gb/s 单位间隔 ps ¼ 单位间隔 ps

46

品导入后继续采取这一措施。不幸的是,它的成本较高。

我的建议是尽量缩小树脂开口、按照与玻纤布相同的间距进行布

线、使用双层玻纤布以及使用低 Dk 玻纤布。

尽量缩小树脂开口

经验丰富的 PCB 制造商和设计团队已经知道某些玻纤布类型

(例如 106 和 1080 玻纤布)不适合高速信号传输。但很少有硬件设

计师和制造商能说出为什么有一些玻纤布比其他的表现更好,以及如

何对它们进行排序。

1080 玻璃纤维布为什

么有对内 Skew 问题? 主要

问 题 是 玻 纤 布 的“树 脂 开

口”(我所命名的术语)比

其他产品更大,例如更薄的

1078 玻纤布或者稍微厚一

些的 1086 玻纤布的树脂开

口都比 1080 小。

图 6.3 展示

的是玻纤覆盖率

(绿色) 与树脂

覆盖率(黄色)

的关系。理想情

况下,为了减轻

玻纤编制效应,

玻纤覆盖率应

尽可能高。更高的玻纤覆盖率意味着差分对中的两条信号路径具有相

同或相似 Dk 环境的可能性更大。

图 6.3 :玻纤布中的树脂开口。

图 6.4 :1080 和 1086 玻纤布树脂开口的对比。

纬纱

间距

经纱

间距

玻纤

纬纱 树脂

宽度

经纱

宽度

树脂

开口

树脂

开口

47

如图 6.4 所示,根据非铺展玻纤布的数据,在 1080 玻纤布中,

树脂开口占电路板面积的 24%(76% 是玻纤布),而 1086 玻纤布的

树脂开口仅为 5%(95% 是玻纤布),而树脂开口越小越好,这个差距

极大。1078 和 1080 玻纤布的差距稍微小一点,但依然差距很大。相

比 1080 玻纤布,这二者都更具有优势。可以用两种常用的方法来量

化不同玻纤布的对内 Skew 相对性能 :光学测量透气性和玻纤布覆盖

率。较低的透气性意味着更高的玻纤覆盖率(高 Dk)和更小的气隙

(具有较低 Dk 的树脂开口)。能够改善玻纤编织效应的最佳玻纤样

式是透气性最低的玻纤布样式。

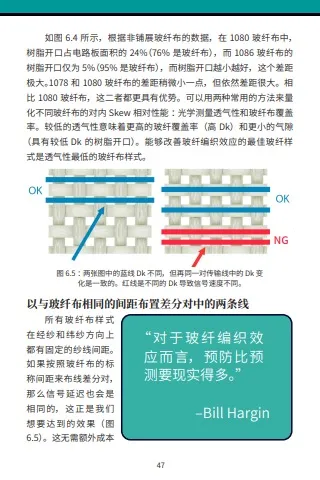

图 6.5 :两张图中的蓝线 Dk 不同,但再同一对传输线中的 Dk 变

化是一致的。红线是不同的 Dk 导致信号速度不同。

以与玻纤布相同的间距布置差分对中的两条线

所有玻纤布样式

在经纱和纬纱方向上

都有固定的纱线间距。

如果按照玻纤布的标

称间距来布线差分对,

那么信号延迟也会是

相 同 的, 这 正 是 我 们

想 要 达 到 的 效 果(图

6.5)。这无需额外成本

“对于玻纤编织效

应而言, 预防比预

测要现实得多。”

–Bill Hargin

NG

48

即可实现。

需要牢记的是,在

使用非正方形玻纤布时,

您需要知道拼版中单板

的方向 ;或者也可以选

择每英寸有对称的两到

四股的玻纤布(不完美,

但总比忽略它好)。

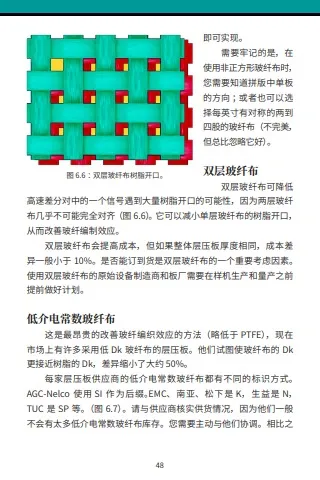

双层玻纤布

双层玻纤布可降低

高速差分对中的一个信号遇到大量树脂开口的可能性,因为两层玻纤

布几乎不可能完全对齐(图 6.6) 。它可以减小单层玻纤布的树脂开口,

从而改善玻纤编制效应。

双层玻纤布会提高成本,但如果整体层压板厚度相同,成本差

异一般小于 10%。是否能订到货是双层玻纤布的一个重要考虑因素。

使用双层玻纤布的原始设备制造商和板厂需要在样机生产和量产之前

提前做好计划。

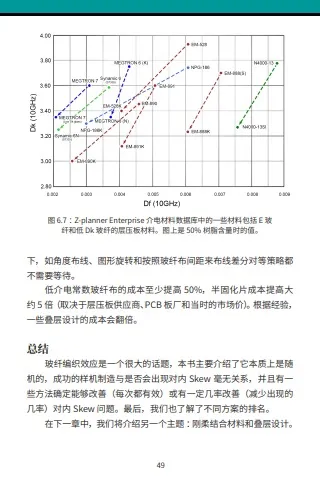

低介电常数玻纤布

这是最昂贵的改善玻纤编织效应的方法(略低于 PTFE),现在

市场上有许多采用低 Dk 玻纤布的层压板。他们试图使玻纤布的 Dk

更接近树脂的 Dk,差异缩小了大约 50%。

每家层压板供应商的低介电常数玻纤布都有不同的标识方式。

AGC-Nelco 使用 SI 作为后缀。EMC、南亚、松下是 K, 生益是 N,

TUC 是 SP 等。(图 6.7)。请与供应商核实供货情况,因为他们一般

不会有太多低介电常数玻纤布库存。您需要主动与他们协调。相比之

图 6.6 :双层玻纤布树脂开口。

49

下,如角度布线、图形旋转和按照玻纤布间距来布线差分对等策略都

不需要等待。

低介电常数玻纤布的成本至少提高 50%,半固化片成本提高大

约 5 倍(取决于层压板供应商、 PCB 板厂和当时的市场价) 。根据经验,

一些叠层设计的成本会翻倍。

总结

玻纤编织效应是一个很大的话题,本书主要介绍了它本质上是随

机的,成功的样机制造与是否会出现对内 Skew 毫无关系,并且有一

些方法确定能够改善(每次都有效)或有一定几率改善(减少出现的

几率)对内 Skew 问题。最后,我们也了解了不同方案的排名。

在下一章中,我们将介绍另一个主题 :刚柔结合材料和叠层设计。

图 6.7 :Z-planner Enterprise 介电材料数据库中的一些材料包括 E 玻

纤和低 Dk 玻纤的层压板材料。图上是 50% 树脂含量时的值。

51

第七章

刚柔结合材料

我职业生涯的大部分时间都在跟刚性 PCB 打交道。刚柔结合板

经常可以在手机中看到。大约六年前,在层压板领域的工作中,我开

始收到对低流动性半固化片的要求,并开始参与流变测试。从那时起,

我学到了更多关于刚柔结合叠层的知识,并在我们的叠层软件解决方

案中加入了对刚柔结合的支持。本章将会分享一些我的经验教训。

柔性和刚柔结合设计是指部分或全部使用柔性基板材料,而不是

完全由刚性基板材料制成的 PCB。柔性材料可以使设计的密度更高,

因为可以三维放置元件和布线并消除物理连接器。这降低了成本并改

善了阻抗连续性,同时提高了可靠性。刚柔结合设计还具有更佳的机

电功能,包括对动态弯曲、振动和冲击的耐受性、耐热性并能够减轻

重量。

更佳的抗冲击和抗振动能力使柔性设计在需要高可靠性的医疗、

汽车、军事和航空航天应用中非常普遍。电路能够部分弯曲可以使设

计的密度更高,因此它在平板显示器和蜂窝移动设备中广泛使用,同

时也使可穿戴技术成为可能。

刚柔结合材料

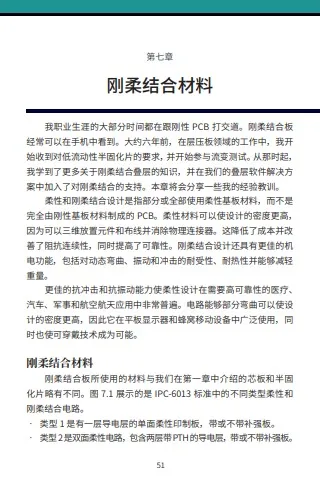

刚柔结合板所使用的材料与我们在第一章中介绍的芯板和半固

化片略有不同。图 7.1 展示的是 IPC-6013 标准中的不同类型柔性和

刚柔结合电路。

• 类型 1 是有一层导电层的单面柔性印制板,带或不带补强板。

• 类型 2 是双面柔性电路,包含两层带 PTH 的导电层,带或不带补强板。

52

IPC ���� 类型 � · 单导电层

· 单侧或双侧有绝缘材料

· 单侧或双侧接入导体

IPC ���� 类型 � · 两个导电层之间有柔性绝缘膜

· 电镀互连孔

· 单侧或双侧有绝缘覆盖材料

· 单侧或双侧接入导体

IPC ���� 类型 � · 三层以上导电层

· 导电层之间有柔性绝缘材料

· 电镀互连孔

· 单侧或双侧有绝缘覆盖材料

· 单侧或双侧接入导体

IPC ���� 类型 � · 两层以上导电层

· 绝缘材料是刚性或柔性的

· 穿过柔性和刚性材料的电镀互连孔

· 穿过单侧或双侧的覆盖材料或 SMOBC 接

入导体

• 类型 3 是多层柔性电路,包含三层或更多带 PTH 的导电层,带

或不带补强板。

• 类型 4 是多层刚性和柔性材料组合,包含三层或更多带 PTH 的

导电层。

• 类型 5 是柔性或刚柔结合电路,包含两层或多层导电层,没有 PTH。

图 7.1 :柔性和刚柔结合 PCB 的类型。

53

刚柔结合设计中的铜以各种方式粘附到柔性电介质材料上。可以

使用粘合剂直接将铜粘合到基材上。有时会添加补强板来加强要放置

元件或布线孔的柔性区域。可以采用电解铜(ED,不太柔软,成本

较低)或压延铜(RA,柔软,成本较高)。柔性平面层通常会被蚀刻

出网格图形,因为铜越少就越柔软。

Coverlay 层是柔性材料,通常位于柔性子叠层的外部。它充当

柔性电路的外保护层,使其绝缘并防止分层。Coverlay 层通常由丙烯

酸、聚酰亚胺和聚酯制成。如图 7.1 所示,典型的 Coverlay 层结构

在顶部有聚酰亚胺电介质,在面向铜的一侧有粘合剂。

粘合层类似于 Coverlay 层,但它们用于内部带状线层,两面都

有粘合剂,中间是聚酰亚胺电介质。将两个柔性芯板粘合在一起,这

就是粘合层的用武之地。

柔性芯板通常会跨越所有子叠层,从铜的一端一直延伸到另一

端。柔性芯板常见的品牌有 DuPont Pyralux 和 Panasonic Felios,

这两个产品系列中有很多不同的产品。无粘合剂的柔性芯板通常用于

高性能刚柔结合应用。有粘合剂的柔性芯板较为便宜,通常用于单面

或双面或低层数的柔性应用。

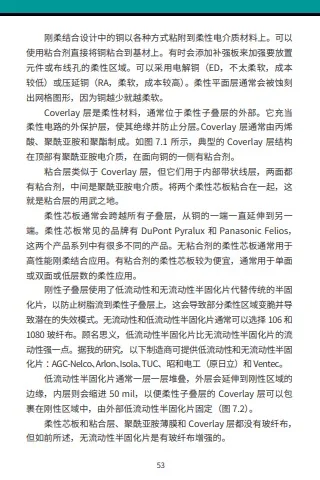

刚性子叠层使用了低流动性和无流动性半固化片代替传统的半固

化片,以防止树脂流到柔性子叠层上,这会导致部分柔性区域变脆并导

致潜在的失效模式。无流动性和低流动性半固化片通常可以选择 106 和

1080 玻纤布。顾名思义,低流动性半固化片比无流动性半固化片的流

动性强一点。据我的研究,以下制造商可提供低流动性和无流动性半固

化片 :AGC-Nelco、Arlon、Isola、TUC、昭和电工(原日立)和 Ventec。

低流动性半固化片通常一层一层堆叠,外层会延伸到刚性区域的

边缘,内层则会缩进 50 mil,以便柔性子叠层的 Coverlay 层可以包

裹在刚性区域中,由外部低流动性半固化片固定(图 7.2)。

柔性芯板和粘合层、聚酰亚胺薄膜和 Coverlay 层都没有玻纤布,

但如前所述,无流动性半固化片是有玻纤布增强的。

54

图 7.2 :柔性子叠层的 Coverlay 层包裹在刚性子叠层的过渡区域中。

设计注意事项

可以根据不同的应用环境选择不同的柔性电路策略。工作温度范

围和持续时间以及对热循环的要求对于是否采用刚柔结合而言至关重

要。

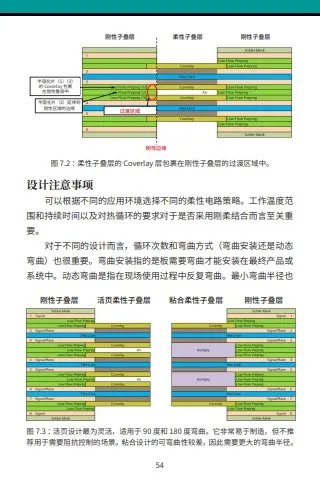

对于不同的设计而言,循环次数和弯曲方式(弯曲安装还是动态

弯曲)也很重要。弯曲安装指的是板需要弯曲才能安装在最终产品或

系统中。动态弯曲是指在现场使用过程中反复弯曲。最小弯曲半径也

图 7.3 :活页设计最为灵活,适用于 90 度和 180 度弯曲。它非常易于制造,但不推

荐用于需要阻抗控制的场景。粘合设计的可弯曲性较差,因此需要更大的弯曲半径。

过渡区域

刚性边缘

刚性子叠层 柔性子叠层 刚性子叠层

半固化片(2)延伸到

刚性区域的边缘

半固化片(1)(3)

的 Coverlay 包裹

在刚性叠层中

刚性子叠层 活页柔性子叠层 粘合柔性子叠层 刚性子叠层

55

是需要考虑的,因为更小的弯曲半径需要更加注意。

在设计刚柔结合项目时,应该考虑到一些重要的与刚性 PCB 不

同的地方。您可以使用活页或粘合方法来连接柔性芯板(图 7.3)。

活页设计会在每个柔性芯板之间留有间隙,这种设计方法更便

宜、更柔软。粘合设计需要对粘合层和半固化片进行额外的层压,会

使设计不那么柔软。虽然它至少比活页设计厚 20 倍,但能改善带状

线的阻抗控制,因为电流返回路径受到了严格控制。

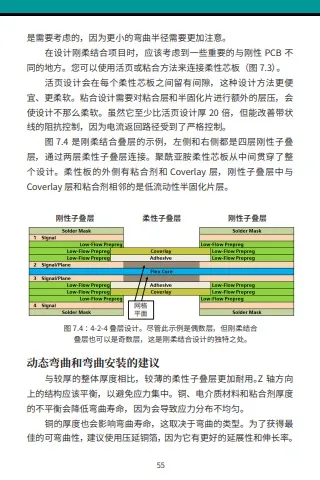

图 7.4 是刚柔结合叠层的示例,左侧和右侧都是四层刚性子叠

层,通过两层柔性子叠层连接。聚酰亚胺柔性芯板从中间贯穿了整

个设计。柔性板的外侧有粘合剂和 Coverlay 层, 刚性子叠层中与

Coverlay 层和粘合剂相邻的是低流动性半固化片层。

动态弯曲和弯曲安装的建议

与较厚的整体厚度相比,较薄的柔性子叠层更加耐用。Z 轴方向

上的结构应该平衡,以避免应力集中。铜、电介质材料和粘合剂厚度

的不平衡会降低弯曲寿命,因为会导致应力分布不均匀。

铜的厚度也会影响弯曲寿命,这取决于弯曲的类型。为了获得最

佳的可弯曲性,建议使用压延铜箔,因为它有更好的延展性和伸长率。

图 7.4 :4-2-4 叠层设计。尽管此示例是偶数层,但刚柔结合

叠层也可以是奇数层,这是刚柔结合设计的独特之处。

刚性子叠层 柔性子叠层 刚性子叠层

网格

平面

56

铜晶粒方向应与导体平行。有刚柔结合业务的供货商知道应该如何处

理这些问题。

弯曲和弯曲动作应尽可能垂直于导体 ;在无法垂直的地方应使用

圆角。如果必须在弯曲部分进行倾斜布线或改变方向,应做成圆角。

并且在弯曲区域不应使用电镀通孔。对于动态弯曲和弯曲安装应用而

言,建议尽可能使用不含粘合剂的材料,因为有粘合剂的材料更容易

疲劳。

柔性参考平面

通常,将网格图案蚀刻到柔性参考平面中以提高可弯曲性。在设

计柔性网格平面时,走线应该在网格交叉处的上方。如果需要受控阻

抗差分对,那么差分对的间距和对角线的间距应该相等。走线应该在

网格交叉处的上方。图 7.5 说明了需要考虑的网格平面参数。

图 7.5 :在此示例中,网格间距为 18。对角线间距为 25.5。网格角度为 45 度,网

格偏移为 1.1 mil ,理想情况下应该为零。(图片来源 :Z-planner Enterprise)

57

最小弯曲半径和失效模式

对于图 7.1 中所示的 1 型和 2 型柔性电路而言,最小弯曲半径应

大于柔性子叠层总厚度的六倍。对于 3 型和 4 型活页柔性电路而言,

最小弯曲半径应大于总厚度的 12 倍,对于 3 型和 4 型带有粘合柔性

层的柔性电路而言,最小弯曲半径应大于总厚度的 20 倍 .

如果不遵循最小半径要求,可能会导致导体断裂、粘合剂和聚酰

亚胺薄膜变形导致开路,或者出现类似刚性板的分层。

柔性电路设计中的“装订”方法会将弯曲外侧的柔性层长度做得

更长,类似于书脊。这是最昂贵的方法,一般只会在尝试过所有其他

90 度或 180 度弯曲的方法都无法实现时才考虑。弯曲区域中图形延

长多少取决于弯曲是 90 度还是 180 度。180 度弯曲意味着长度是原来

的两倍,这会大幅提高制造成本。

IPC-2223 中重点介绍了首选的和不适当的弯曲区域布线实践。

一些比较重要的示例如下 :

• 避免改变弯曲区域的走线宽度,应在整个弯曲区域内保持相同的

宽度。

• 均匀分布走线。对称性不佳会增加应力集中的可能性。

• 垂直于弯曲区域布线。

• 不要在弯曲区域放置导通孔。

58

59

在 我 研 究 生 毕 业 后 的 30 多 年 中, 我 曾 多 次 与 Eric Bogatin、

Happy Holden、Lee Ritchey、Howard Johnson 和 Rick Hartley 等行

业资深人士进行交流,虚心受教。撰写本章的目的是希望我的一些经

验会对大家有所帮助,将这本书的内容联系起来,并加入一些从业务

视角出发的有关 PCB 叠层设计的内容。

有一句话是这么说的 :“人人都愿意夸耀成功,而没人愿意承认

失败。” 我认为对于产品和项目都是如此。每个人都喜欢跟成功的产

品或项目沾点边,希望能从中获得一些政治资本。在我看来,我们可

以在事后对失败、延迟和不完美进行分析,从中学到更多知识和经验,

而不是去蹭成功的热度。

我们总是希望改善“上市时间”,但它的具体含义是什么? 首先,

它是包含了质量、可靠性、进度和成本在内的总体优化过程的一部分。

图 8.1 展示的是 PCB 叠层设计与这三个产品目标之间的重叠关系。

理想情况下,公司希望制造出客户愿意支付更高价格的创新性或

高质量产品,并且最好是在竞争对手推出之前。我们希望最大限度减

少实现这一目标所需的时间 :减少上市时间 (TTM) 。虽然我们要快

速达到这一目标,但还是不能忽视质量和利润因素。平均下来,产品

会因上市时间过晚而损失一半的利润,有时甚至会高达 100%。

回想一下,黑白电视机花了 20 多年的时间才达到 100 万台的总

销量。彩色电视机只用了 13 年。如今,一些家用游戏机第一个月就

第八章

总结

60

可以销售超过 100 万台。上市时间比以往任何时候都更加重要。

在第三章和第四章中,我们探讨了过度设计和欠设计与材料选择

的关系。工欲善其事,必先利其器,根据我的经验,如果提前做好计

划和损耗规划,就可以节省超过 10% 的裸板成本。

上市时间中的一部分还与质量和可靠性有关。产品可能会由于

质量问题而延迟上市,或者最坏的情况是出现大量现场失效。我曾经

协助过会莫名其妙出现现场失效的项目。这些设计无一不存在一些问

题,包括一些与端接策略和叠层相关的阻抗失配。现场失效所造成的

损失通常都是天文数字,是一定要避免的。

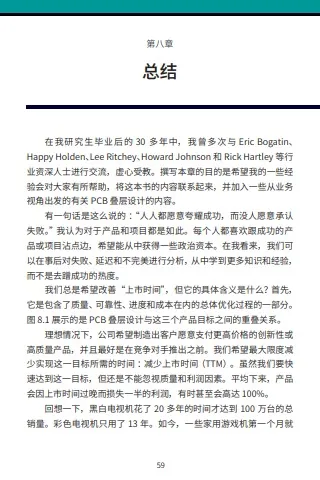

由克莱斯勒进行的研究表明,在设计过程的早期做出设计决策的

成本是在流程的后一个阶段再进行修改的成本的 10%。通过采用这

一原则,克莱斯勒实现了行业领先的单台车盈利能力。图 8.2 显示了

这种关系,称为“10 倍法则”。

自从我读到《第一次就做好,高速 PCB 和系统设计实用手册》

质量 和

可靠性

上市时间

排程和

成本

· 上市时间

· 可预测的进度

· 设计和样机重新设计

· 缩小的市场窗口

· 盈利能力

· 机会成本

· 用于信号完整性仿真的

准确叠层参数

· 材料选择和损耗优化

· 热可靠性和认证

· 现场故障风险

· 材料/裸板制造成本

· 设计过度/不足的风险

· 设计耗时过多效率低下

· 样机成本

影响结果的关键叠层设计问题

叠层设计

图 8.1 :能够降低成本的叠层设计的关键问题。

61

中 Lee Ritchey 所写的一句

话后,这句话就一直萦绕在

我心头。

“工程师们会设计各种

创新的、巧妙的产品,但通

常不知道成本是多少,而且

似 乎 并 不 关 心 这 一 点, 认

为成本控制并不是工作的一

部分。这些工程师掌握着公

司 的 财 务 成 败, 但 似 乎 他

们并不知道这一点。” - Lee

Ritchey

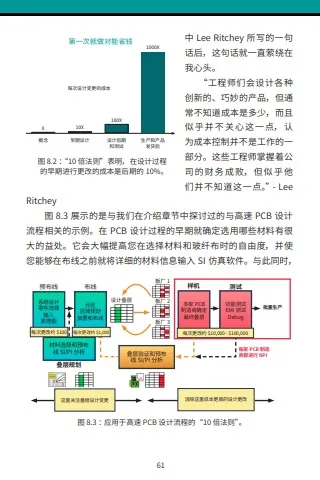

图 8.3 展示的是与我们在介绍章节中探讨过的与高速 PCB 设计

流程相关的示例。在 PCB 设计过程的早期就确定选用哪些材料有很

大的益处。它会大幅提高您在选择材料和玻纤布时的自由度,并使

您能够在布线之前就将详细的材料信息输入 SI 仿真软件。与此同时,

X

概念 早期设计 设计后期

和测试

生产和产品

发货后

10X

100X

1000X

每次设计变更的成本

第一次就做对能省钱

系统设计 设计叠层

零件选择

输入

原理图

预布线

分区

区域规划

放置和布线

布线

板厂 1

板厂 2

板厂 3

多家 PCB

制造商确定

最终叠层

样机 测试

功能测试

EMI 测试

Debug

批量生产

每家 PCB 制造 叠层验证和预布 商都进行 NPI

线 SI/PI 分析

材料选择和预布

线 SI/PI 分析

叠层规划

系统设计 设计叠层

零件选择

输入

原理图

预布线

分区

区域规划

放置和布线

布线

板厂 1

板厂 2

板厂 3

多家 PCB

制造商确定

最终叠层

样机 测试

功能测试

EMI 测试

Debug

批量生产

每家 PCB 制造 叠层验证和预布 商都进行 NPI

线 SI/PI 分析

材料选择和预布

线 SI/PI 分析

叠层规划

每次更改约 $100 每次更改约 $1,000 每次更改约 $10,000 - $100,000

这里关注叠层设计变更 消除这里成本更高的设计更改

图 8.2 :“10 倍法则”表明,在设计过程

的早期进行更改的成本是后期的 10%。

图 8.3 :应用于高速 PCB 设计流程的“10 倍法则”。

62

采购部门可以开始与不同的 PCB 板厂进行谈判,为样机和批量生产

制定材料计划,从而将 NPI 流程缩短数周甚至数月。

通过将材料选择和叠层设计尽可能地左移,我们在流程前期确

定材料,这样,跟板厂确定叠层规格可能只需要不到 10 小时的时间,

每小时花费大约 100 美元。然而,在我所见过的另一个极端案例中,

在两周多的时间里,PCB 板厂在样机和生产之前与硬件团队进行了多

达 75 次设计更改。同样的任务从花费数百美元变成花费数千美元。

没有库存的材料的正常周转时间为六周。当我在层压板行业工

作时,每隔一段时间就会收到电子邮件和电话,要求我们加急订单并

今早发货来帮助某些公司进行样机制造。尽快锁定“规格”和“加工”

叠层并让硬件设计人员控制流程可以为您争取到时间表上的一个月甚

至更长的时间,同时实现更准确且更真实的信号完整性仿真。如果能

减少一次样机改版,就能把上市时间缩短六周以上。

设计中的设计

最后,我想重申书中提出的几个重点。

1. 叠层设计会影响 PCB 上的每个信号。

2. 制造的物理世界与您的设计中的电气完整性不断在发生冲突。

3. 如果您的设计遇到信号完整性问题,它几乎总是与您输入到信号

完整性仿真中的叠层或叠层参数有关。

4. 研发人员需要将详细的叠层和材料决策左移到设计过程的早期阶

段。

在过去的五年中,我们一直在开发 Z-planner Enterprise 软件,

以服务于本书中所谈到的目的和流程。

这就是设计中的设计。

63

“在电介质厚度、介电

特 性( 如 Dk 和 Df )、

走线宽度和间距都不知

道的时候完成一堆仿真

有什么意义?”

- Bill Hargin

64

65

参考文献

Lee Ritchey (2015) , “Minimizing Skew in High Speed Differential

Links,” Speeding Edge.

Scott McMorrow, et al. (2005) , “Impact of PCB Laminate Weave

on Electrical Performance,” DesignCon.

Lee Ritchey (2007) , “A Way to Address the Problem of Jitter and

Skew in Gigabit and Faster Signals Caused by Laminate Weaves,”

Current Source, June.

Eric Bogatin (2005) , “Skewering Skew—Laminate Weave Induces

Skew,” Printed Circuit Design, April.

Jeff Loyer, et al. (2007) , “Fiber Weave Effect: Practical Impact,

Analysis and Mitigating Strategies,” DesignCon.

Eric Bogatin, Bill Hargin, et al. (2017) , “New Characterization

Technique for Glass-Weave Skew,” DesignCon.

Bill Hargin (2016) , Chapter 20, “Electrical and Mechanical Design

Parameters,” Chapter 20, Printed Circuits Handbook, Seventh

Edition, McGraw-Hill Education, Editors Clyde Coombs and Happy

Holden.

Bill Hargin (2020) , “Etch Effects Explained,” Printed Circuit

Design & Fabrication, December.

Bill Hargin (2020) , “Actual Copper Thicknesses,” Printed Circuit

Design & Fabrication, August.

Happy Holden, e-mail correspondence, December 2020.

Bill Hargin (2021) , “Winning the War Against Analysis Paralysis,”

Printed Circuit Design & Fabrication, February.

67

Z-zero

Z-zero, LLC 位于华盛顿州雷德蒙德 , 公司提供全面的软件解决

方案,以缩小硬件设计团队与 PCB 制造商之间的差距。Z-zero

软件的外观和感觉都是按照电子表格来设计的,它使硬件设计

团队能够在传统 PCB 设计流程中自动执行叠层设计和材料选

择。如需了解更多信息或下载免费评估的软件和叠层设计教

程,请访问 z-zero.com。

西门子数字化工业软件

西门子数字化工业软件致力于推动数字化企业转型,实现满足

未来需求的工程、制造和电子设计。我们的解决方案组合可帮

助各类规模的企业创建并充分利用数字化双胞胎,为企业带来

全新的洞察、机遇和自动化水平,促进创新。更多有关西门子

数字化工业软件的产品和服务的信息,请访问 siemens.com/

software 或关注我们的领英、推特、Facebook 和 Instagram。

西门子数字化工业软件——数智今日,同塑未来。

关于 Z-zero 和

西门子数字化工业软件

PCB 叠层设计

设计中的设计

PCB 中所包含的叠层需要单独的设计过程, 在典型的

PCB 设计中,它总是被忽略。如今,信号速度呈指数级增长,

这使得叠层设计与布局过程一样重要,从而确保您的要求得

到满足。

西门子 Z-planner Enterprise 可以进行布局前 SI 仿真,在

初始 PCB 设计阶段尽早验证您的叠层设计和材料,从而节省

时间,并从第一天起就开始优化电路板性能。

高速叠层设计

Z-planner Enterprise 是一款叠层规

划工具, 其中包含了 PCB 叠层计算

器和强大的材料库, 专注于阻抗和信

号完整性。 它能为整个工作流程都提

供益处,并且能够直接集成到您目前

的设计工作流程中。

该页无缩略图

该页无缩略图